这是SemiAnalysis最新的一篇GTC大会的分析文章,难得Dylan这么勤快,在GTC放发布后,就立马出了这篇长达31页的分析报告。

报告内容非常全面,针对GTC上老黄的演讲,分析了NVIDIA在硬件和软件方面的创新,以推动AI模型的训练和部署。报告中也多次提到了NVIDIA 如何通过其硬件和软件解决方案支持 DeepSeek 的 AI 模型训练和推理方面。

都说Deepseek出来之后,不需要那么大的算力,到底会不会利空英伟达?现在英伟达还是不是金字塔尖的唯一存在?这篇报告中都给出了分析。

这么硬核的报告,我们就把全文内容整理出来了,而不只是总结。

内容很长,希望大家耐心看完。

高浓度的主流模型(如 DeepSeek 等)开发交流;

资源对接,与 API、云厂商、模型厂商直接交流反馈的机会;

好用、有趣的产品/案例,Founder Park 会主动做宣传。

01

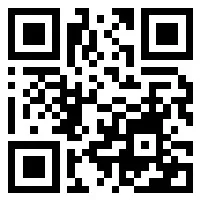

推理token的大爆炸

Claude 3.7在软件工程方面展现出了惊人的性能。Deepseek v3表明上一代模型能力的价格正在暴跌,从而推动了其进一步应用。OpenAI的o1和o3模型显示,更长的推理时间和搜索意味着更好的答案。就像预训练定律的早期一样,对于这些模型的训练后增加更多计算似乎没有限制。今年的GTC(英伟达技术大会)专注于实现智能和token数量的爆发式增长。英伟达正专注于将推理成本大幅降低35倍,以实现模型的训练和部署。

去年的口号是“买得越多,省得越多”,但今年的口号是“省得越多,买得越多”。英伟达在硬件和软件方面的路线图所提供的推理效率,解锁了在经济高效的模型部署及其他变革性企业应用中的推理能力和智能体应用,使其得以广泛传播和应用——这是杰文斯悖论的一个典型例子。或者正如老黄所说:“买得越多,造得越多”。

市场对此感到担忧。人们担心DeepSeek式的软件优化以及英伟达推动的硬件持续改进带来了过多的节省,这意味着对人工智能硬件的需求会减少,市场将出现token过剩的情况。价格确实会影响需求,随着智能服务价格的下降,智能能力的前沿不断拓展,然后需求就会增加。如今,由于推理成本的限制,人工智能的实际应用受到了成本制约。人工智能对我们生活的实际影响仍处于起步阶段。随着成本下降,净消费量反而会矛盾性地增加。对token通缩的担忧类似于只讨论光纤泡沫时期每包互联网连接成本下降,却忽略了网站和互联网驱动的应用程序最终会对我们的生活、社会和经济产生的影响。关键区别在于带宽需求是有限的,而随着能力大幅提升和成本下降,对智能的需求会无限增长。英伟达提供了支持杰文斯悖论的数据。如今模型需要处理超过100万亿个token,推理模型的token数量是之前的20倍,计算量是之前的150倍。

02

Jensen Math 的变化

老黄(Jensen)每年都会给行业带来新的数学规则。Jensen math 以其令人费解而闻名,今年又增添了新的规则。

这里我们解释一下:老黄在介绍公司产品和技术指标时所使用的一些独特的计算方式和规则,这些方式有时会让外界感到困惑,因此被调侃为 “Jensen math”。

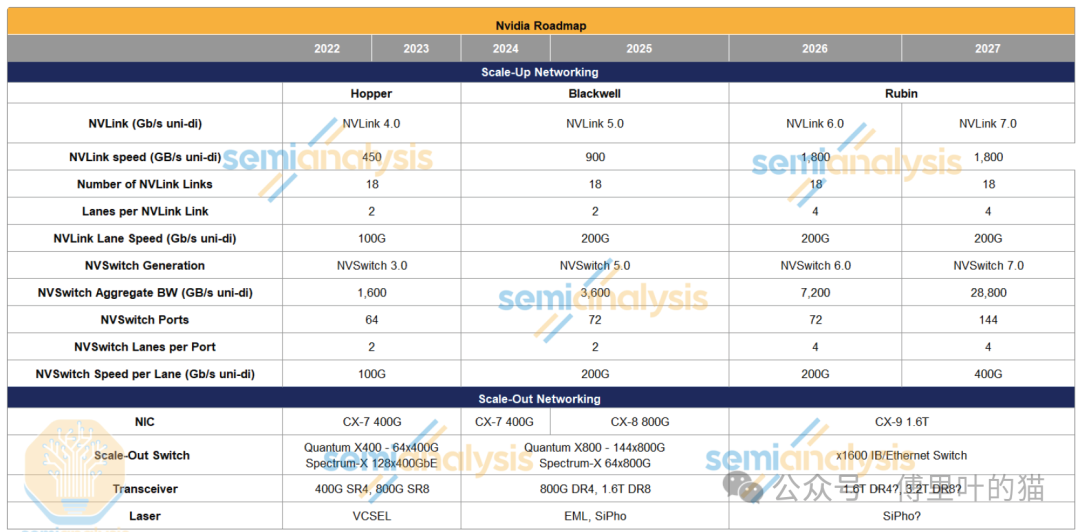

第一条Jensen math规则是,英伟达(Nvidia)公布的浮点运算次数(FLOPs)是基于2:4稀疏度(但没人使用这种稀疏度)来计算的,而不是基于密集浮点运算次数(这是现实世界中的性能衡量指标)。也就是说,H100的FP16(半精度浮点数)的989.4万亿次浮点运算被宣称是1979.8万亿次浮点运算 。

第二条Jensen math规则是,带宽应以双向来表述。NVLink5的带宽被标为1.8太字节/秒(TB/s),因为它的发送带宽是900吉字节/秒(GB/s),接收带宽也是900GB/s ,这两个数值相加就得到了规格表上的数据。但在网络领域,标准做法是标注单向带宽。

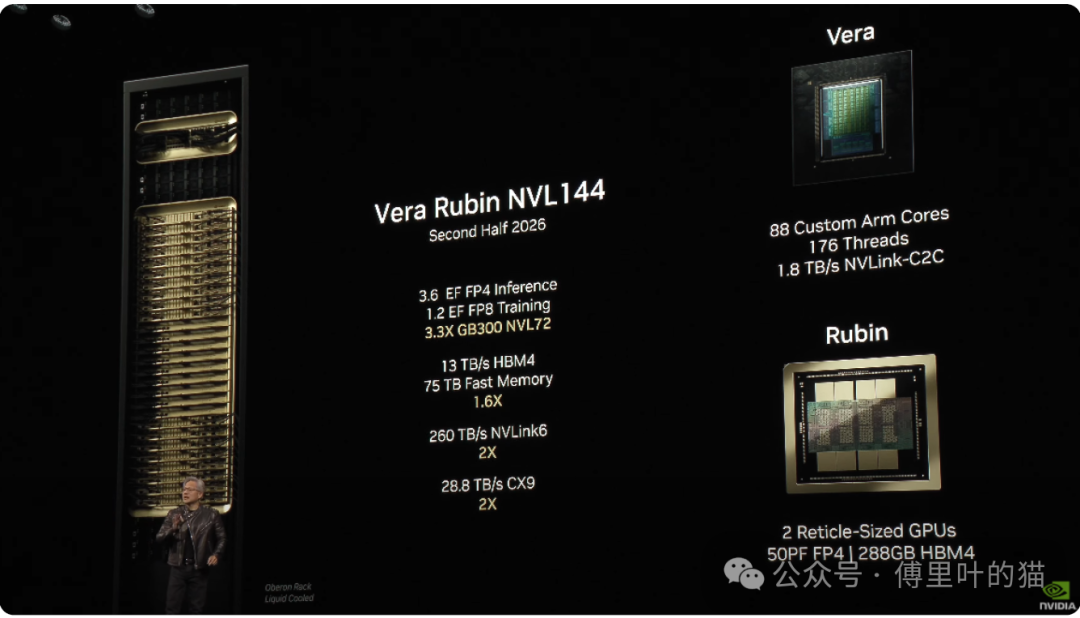

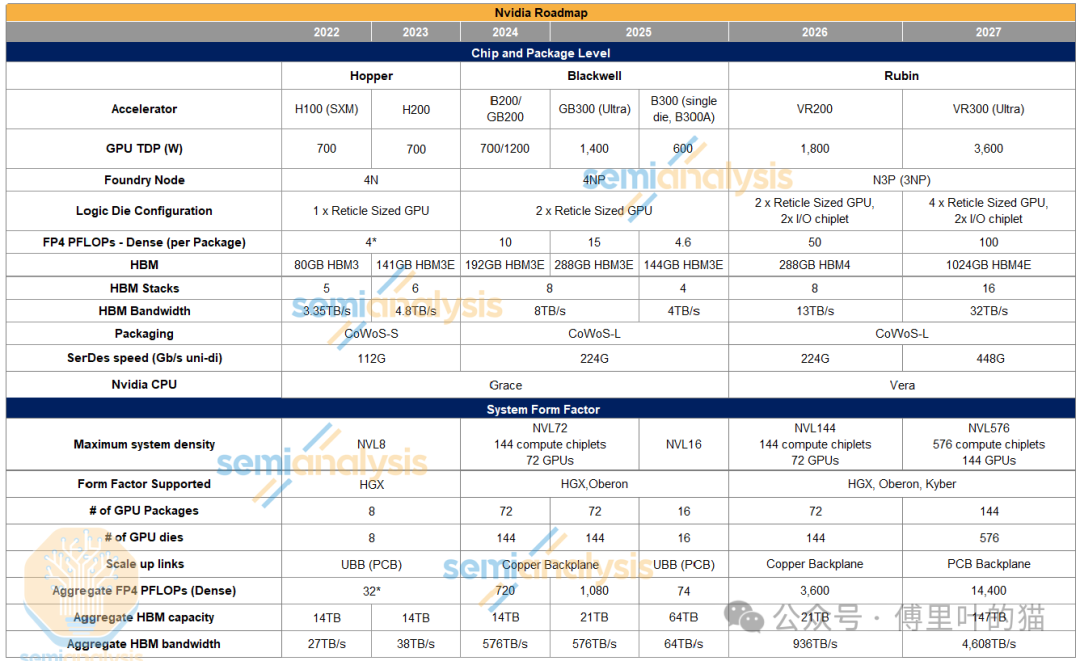

现在,第三条Jensen math规则出现了。GPU的数量将以封装内的GPU芯片(die)数量来计算,而不是以封装的数量来计算。从Rubin系列开始将采用这种命名方式。第一代Vera Rubin机架将被称作NVL144 ,尽管其系统架构与GB200 NVL72类似,有着相同的Oberon机架和72个GPU封装。第一代Vera Rubin机架将被命名为NVL144 ,尽管其系统架构与GB200 NVL72类似,有着相同的奥伯龙机架和72个GPU封装。这对所有人来说都很难理解,并且会不断引发需要澄清的问题 ,但无奈我们都生活在老黄的世界里 。

03

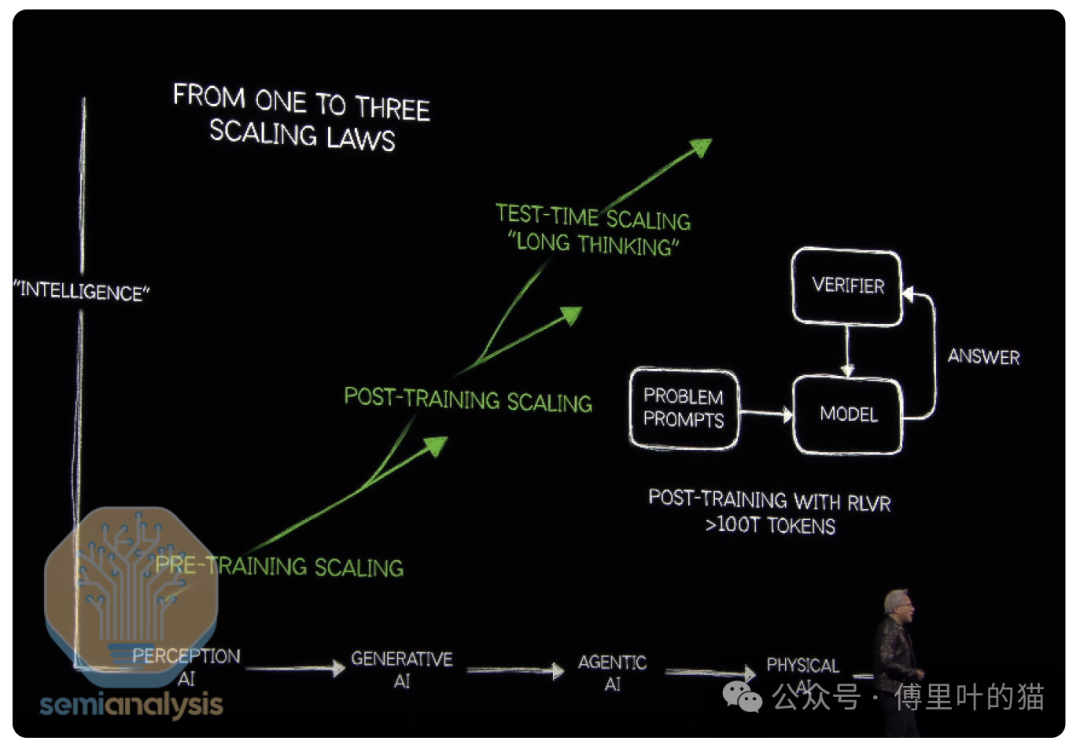

GPU 和系统路线图

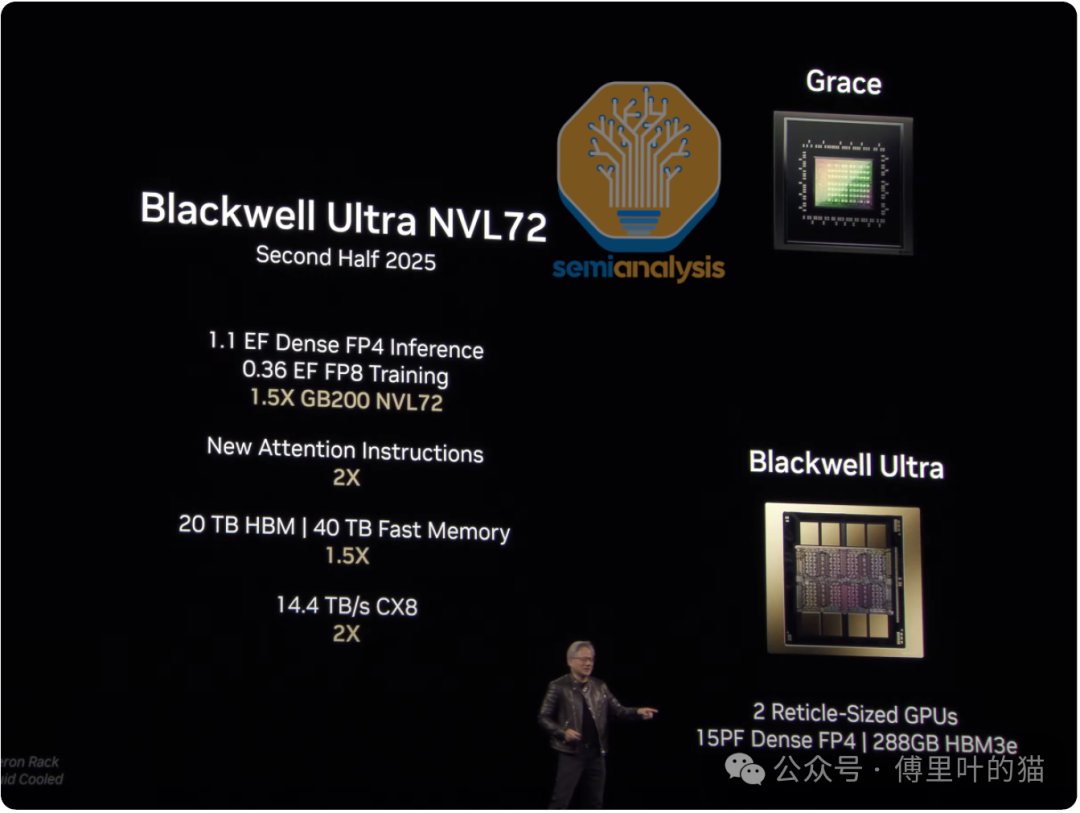

现在,让我们来回顾一下产品路线图。

04

Blackwell Ultra B300

这是通过减少许多(但不是全部)FP64 ALU,并用FP4和FP6 ALU替代它们来实现的。双精度工作负载主要用于HPC和超级计算工作负载,而非AI工作负载。虽然这让HPC社区感到失望,但Nvidia从商业角度出发,着重强调AI,因为这是更重要的市场。

B300 HGX版本现在被称为B300 NVL16。这将采用之前所称的Blackwell“B300A”单GPU变体,现在重命名为“B300”。它是双芯片B300的一半,并且由于普通B300单个封装内没有将两个GPU芯片连接起来的高速D2D接口,所以可能会有更多的通信开销。

B300 NVL16将取代带有16个封装及位于底板上的GPU芯片的B200 HGX外形规格。为实现这一点,在8个可插拔SXM模块(每个模块上有2个这种单芯片封装)中放置了2个这种单芯片封装。目前尚不清楚Nvidia为何选择这条路线而非坚持使用8×双芯片B300;我们推测,更小的CoWoS模块和封装基板带来的良率提升是一个关键驱动因素。请注意,封装技术将采用CoWoS-L而非CoWoS-S。这是一个重要的决定。CoWoS-S的成熟度和产能是之前采用单芯片B300A的原因。这种转变表明CoWoS-L已经迅速成熟,其良率相比CoWoS-L初期不稳定时已趋于稳定。

这16个GPU将通过NVLink协议进行通信,并且与B200 HGX一样,在两组SXM模块之间会有两个NVSwitch 5.0 ASIC。

最后,有一个新细节是,与前几代HGX不同,B300 NVL16不会配备Astera Labs的重定时器。不过,一些超大规模数据中心运营商会选择安装PCIe交换机。

05

Rubin Specifications

Rubin将提供惊人的50 PFLOPs密集FP4计算能力,相比B300实现了三代以来超过三倍的提升。Rubin是如何做到这一点的呢?Nvidia在几个重要方面进行了拓展:

如上所述,I/O芯片释放了空间,可能有20-30%的区域可用于更多的流式多处理器和张量核心。 Rubin将采用3nm工艺制造,使用Nvidia定制的3NP工艺或标准N3P工艺。从Blackwell一代的3NP到4NP,逻辑密度大幅提升,但SRAM几乎没有缩小。 此外,Rubin的TDP将更高——我们估计为1800W,这甚至可能使时钟频率进一步提高。 接下来是架构扩展。Nvidia在每一代中都会为张量核心使用越来越大的脉动阵列。我们认为,从Hopper代的32×32增加到Blackwell代的64×64,对于Rubin来说可能会增大到128×128。更大的脉动阵列能实现更好的数据复用并降低控制复杂度,通常在面积和功耗方面也更高效。不过,对它们进行编程更具挑战性,这也是为什么Nvidia没有像Google在其TPU上那样做到256×256那么大的原因。而且这对制造良率也有不利影响。Nvidia对于光罩尺寸的单片芯片有非常高的参数良率,因为其架构中内置了冗余性和可修复性,许多较小的计算单元即使有缺陷也能被禁用,从而实现良率提升。这与TPU不同,TPU的张量核心数量较少但体积非常大,不具备修复有缺陷逻辑单元的相同能力。

这就是新命名方式出现的地方。尽管新的机架有72个GPU封装,但由于每个封装有2个计算芯片,总共144个计算芯片(72个封装×每个封装2个计算芯片),所以这个新机架将被命名为VR200 NVL144。Nvidia真是一家具有创新精神的公司,甚至连我们对GPU的计数方式都改变了!AMD的市场营销团队应该引以为鉴。AMD没有宣称MI300X系列可以扩展到64个GPU的世界规模(每个系统8个封装×每个封装8个XCD小芯片),这错失了一个关键机会。

Nvidia的HBM容量将保持逐代288GB不变,但升级到了HBM4:8组12-Hi,每层存储密度仍为24GB。转向HBM4带来了带宽提升,总带宽达到13TB/s,主要是由于总线宽度加倍至2048位,引脚速度为6.5Gbps,这是当前JEDEC标准的极限。

回到Oberon,背板仍将采用相同的铜背板,但我们认为其电缆数量将按比例翻倍,以匹配每个GPU通道数量的翻倍。

在NVSwitch方面,NVSwitch ASIC的总带宽也将翻倍,同样是通过通道数量的翻倍实现的。

06

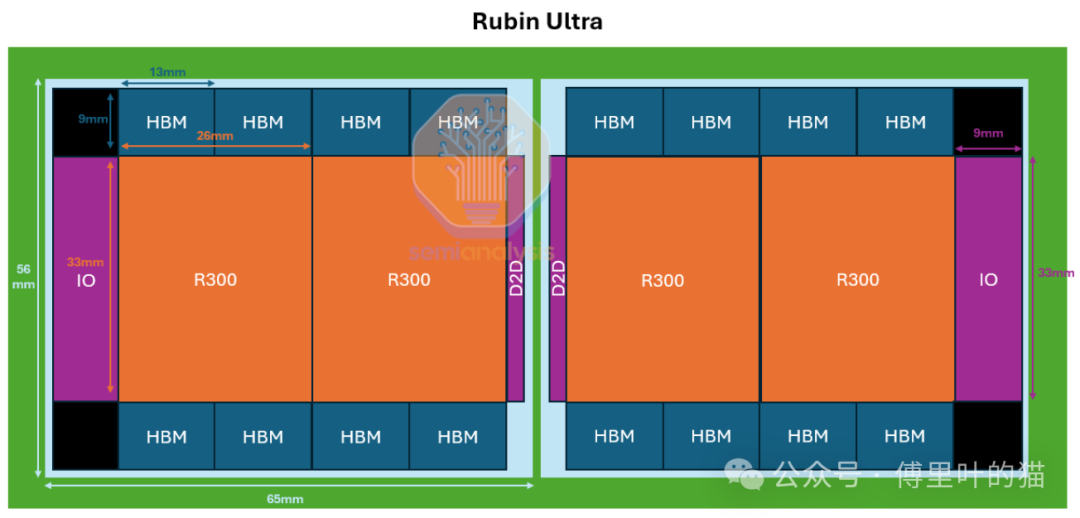

Rubin Ultra Specifications

我们认为,为了避免使用单个超大尺寸的中介层(接近 8 倍光罩尺寸),该封装将采用两个中介层分布在基板上。中间的两个 GPU 芯片将通过一个带有 D2D 接口的薄 I/O 芯片相互通信,并通过基板进行通信。这将需要一个超大的 ABF 基板,超出了当前 JEDEC 封装尺寸的限制(宽度和高度均为 120mm)。

系统总共有 365TB 的快速内存/二级 LPDDR。每个 Vera CPU 配备 1.2TB 的 LPDDR,总共 86TB(72 个 CPU),其余部分则由每个 GPU 封装配备 2TB 的 LPDDR 来补充。这是定制 HBM 基础芯片功能的实现。LPDDR 内存控制器被放置在基础芯片上,以增加这种额外的二级内存,这些内存位于封装旁边的 LPCAMM 模块上。这是 Vera CPU 自带的二级内存之外的补充。

07

Kyber 机架架构

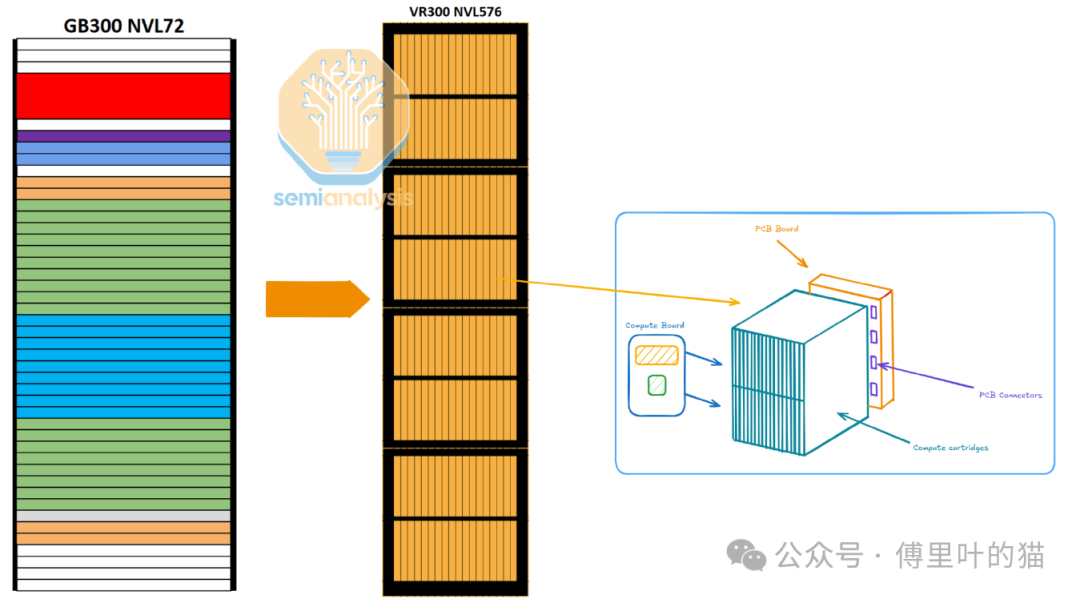

一个关键的新特性是 Kyber 机架架构。Nvidia 通过将机架旋转 90 度来提高密度。考虑到 NVL576(144 个 GPU 封装)配置,这是大规模扩展世界中密度提升的又一惊人举措。

计算托盘旋转90度:为了实现更高的机架密度,计算托盘被旋转90度,采用墨盒形式。 每个机架包含4个罐体:每个罐体包括两层,每层有18个计算墨盒。 NVL576配置:每个计算墨盒中有一个R300 GPU和一个Vera CPU。 每个罐体总共有36个R300 GPU和36个Vera CPU。 NVLink世界规模:总共144个GPU(576个芯片)。 PCB背板替代铜缆背板:作为GPU与机架内NVSwitch之间的扩展链路,PCB背板取代了铜缆背板。这一转变主要是由于在更小的空间内布置电缆的难度增加。

有趣的是,供应链中有迹象表明存在VR300 NVL1,152(288个GPU封装)的Kyber机架变体(如果你计算上面GTC主题演讲中展示的晶圆,你会看到标红的288个GPU封装)。我们认为这可能是一个正在开发的潜在SKU,它将使机架密度和NVLink世界规模从GTC 2025展示的NVL576(144个GPU封装)翻倍到未来的NVL1,152(288个封装)。

此外,还将推出新的第七代NVSwitch,这一点值得注意。这是NVSwitch首次在平台中期推出。这使得交换机聚合带宽和基数能够扩展到单个域中的576个GPU芯片(144个封装),尽管拓扑结构可能不再是全对全非阻塞的优化单层多平面拓扑,而可能是多平面优化的两层网络拓扑,甚至是非闭合拓扑。

08

Blackwell Ultra 的硬件改进

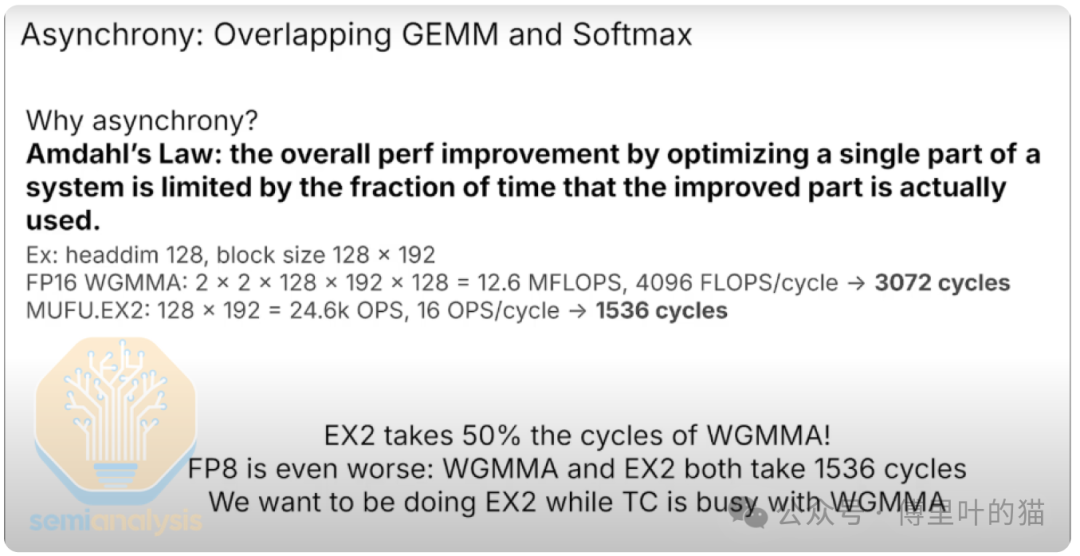

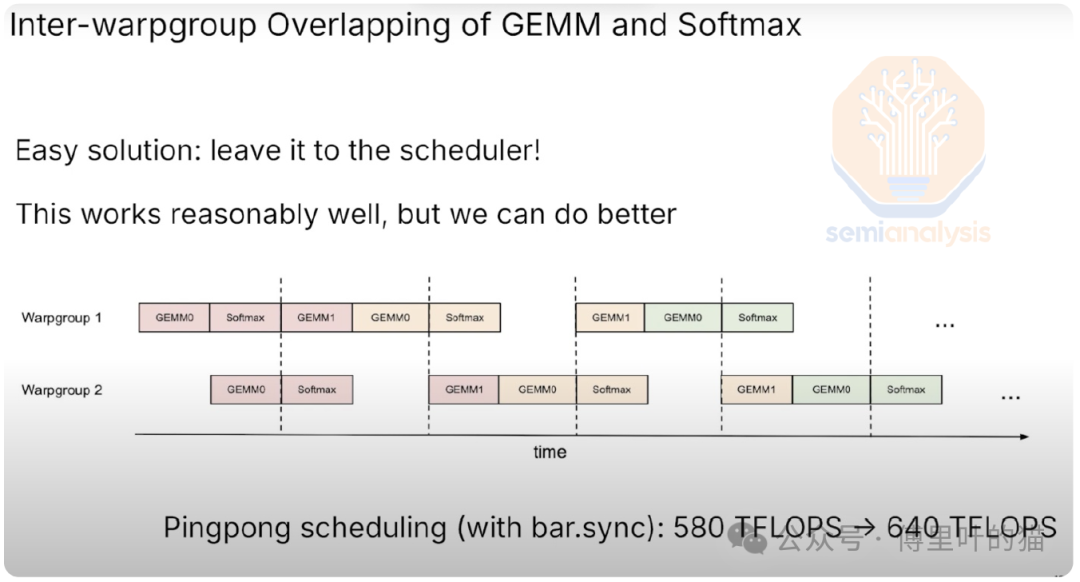

所有类型的注意力机制,如flash-attention、MLA、MQA和GQA,都需要矩阵乘法(matmuls)和softmax函数(行归约和逐元素指数函数)。矩阵乘法被称为GEMM(通用矩阵乘法),仅适用于神经网络计算中的矩阵乘法部分。

在GPU中,GEMM在张量核心上执行。张量核心每一代都在变得更快,但专注于逐元素指数计算(softmax)的多功能单元(MUFU)的性能并没有每一代都显著提升。

在Hopper的bf16(bfloat16)上,计算注意力层中的softmax需要消耗GEMM 50%的周期。这需要内核工程师通过重叠来“隐藏”softmax的延迟,使得编写内核变得具有挑战性。

在Hopper的FP8(浮点)上,计算注意力层中的softmax消耗的周期数与GEMM完全相同。这意味着如果你完全不进行任何重叠,注意力层的耗时将翻倍。具体来说,计算matmul需要约1536个周期,然后计算softmax也需要1536个周期。这就是重叠提高吞吐量的地方。由于softmax和GEMM消耗的周期数相同,内核工程师需要优化一个完美的重叠内核。然而,现实中无法做到完美重叠,硬件性能会因Amdahl定律而损失。

我们迄今为止描述的挑战主要是在Hopper GPU世界中。这个问题在第一代Blackwell中也存在。Nvidia通过Blackwell Ultra重新设计了SM并添加指令来解决这个问题。

这正是Nvidia新的推理栈和Dynamo发挥作用的地方。

09

推理栈与Dynamo

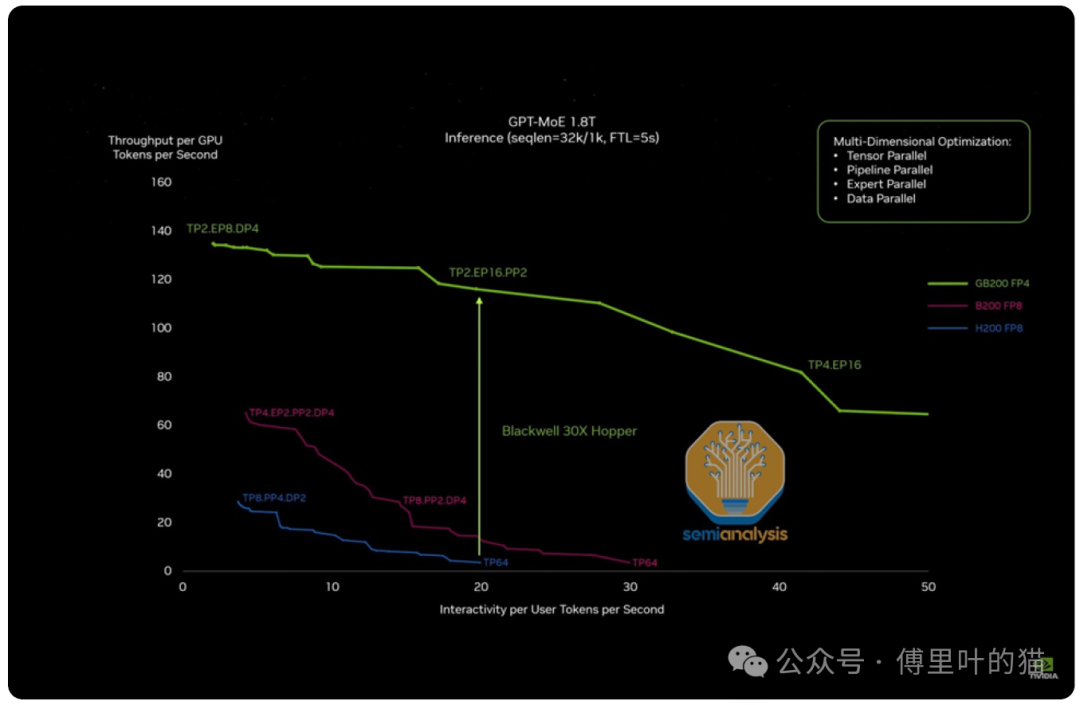

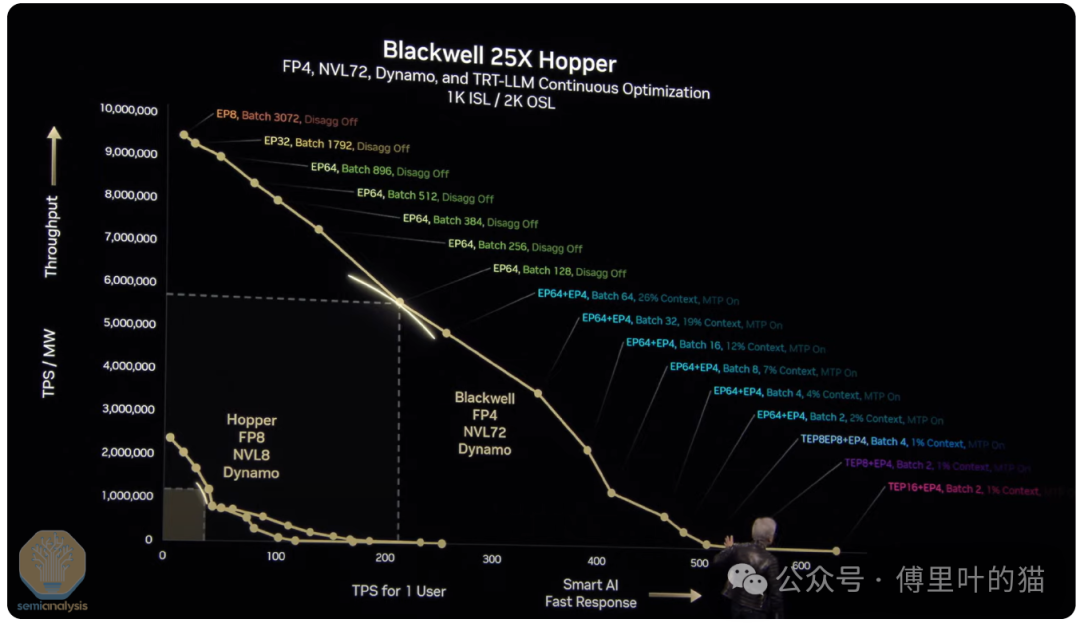

在去年的GTC上,Nvidia讨论了GB200 NVL72的72-GPU扩展世界规模如何使其在FP8下的推理吞吐量相比H200提升了15倍。

Blackwell Ultra GB300 NVL72相比GB200 NVL72提供了50%更高的FP4密集PFLOPs性能,同时HBM容量也增加了50%——这两者都将提升推理吞吐量。路线图中还包括Rubin世代网络速度的多项升级,这些也将显著提升推理吞吐量。

硬件方面的下一次推理吞吐量飞跃将来自Rubin Ultra的扩展网络世界规模,从Rubin的144个GPU芯片扩展到576个GPU芯片。而这仅仅是硬件改进。

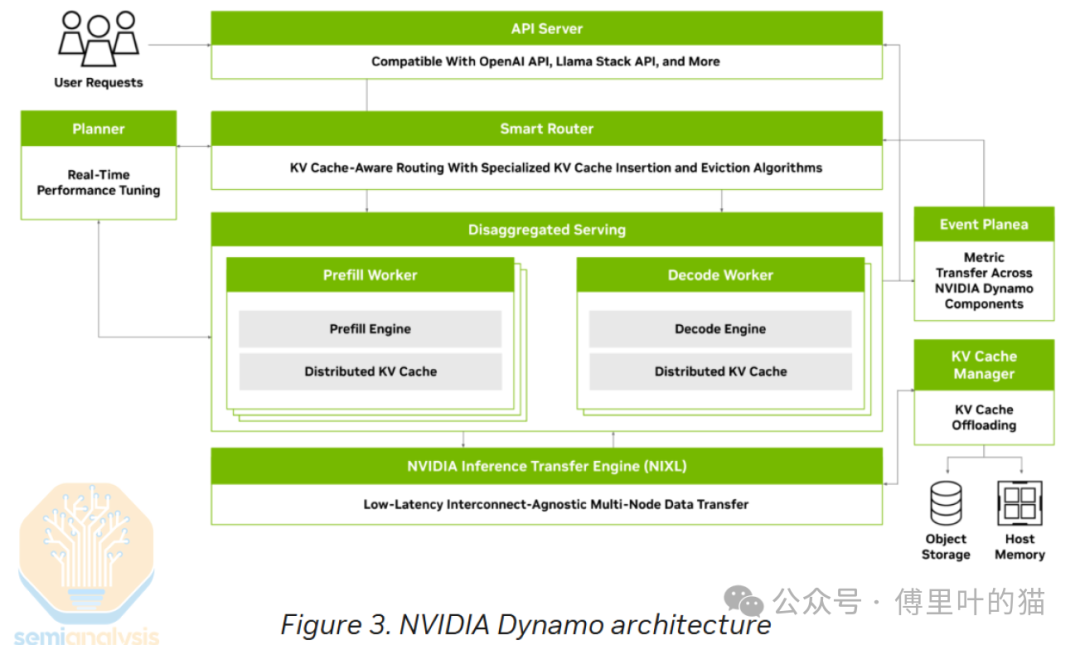

在软件领域,Nvidia宣布了Nvidia Dynamo——一个专注于简化推理部署和扩展的开放AI引擎栈。它有可能颠覆VLLM和SGLang,提供VLLM所不具备的多种功能,并以更高的性能运行。结合硬件层面的创新,Dynamo将再次推动吞吐量与交互性曲线的右移——特别是在高交互性用例中提升吞吐量。

智能路由器(Smart Router) GPU规划器(GPU Planner) 改进的NCCL集体通信(Improved NCCL Collective for Inference) NIXL——NVIDIA推理传输引擎(NIXL – NVIDIA Inference Transfer Engine) NVMe KV缓存卸载管理器(NVMe KV-Cache Offload Manager)

10

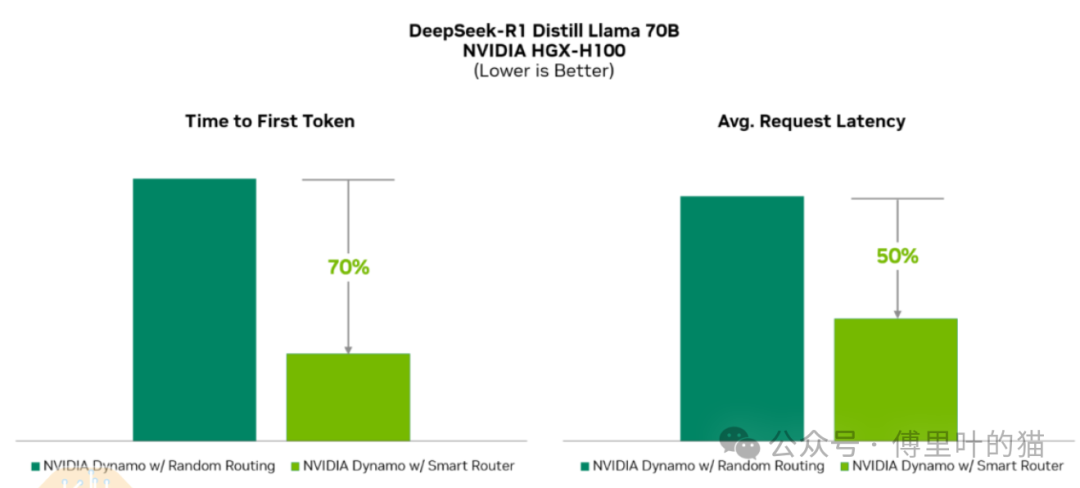

智能路由器(Smart Router)

智能路由器在多GPU推理部署中智能地将每个token路由到预填充(prefill)和解码(decode)GPU。对于预填充阶段,这意味着确保传入的token均匀分布到负责预填充的不同GPU上,以避免在预填充阶段的任何专家上出现瓶颈。

同样,在解码阶段,确保序列长度和请求在负责解码的GPU之间得到良好分布和平衡也很重要。流量较大的专家也可以通过GPU规划器进行复制,以帮助保持负载平衡。

路由器还在每个服务模型的副本之间进行负载平衡,这是vLLM和许多其他推理引擎所不支持的功能。

11

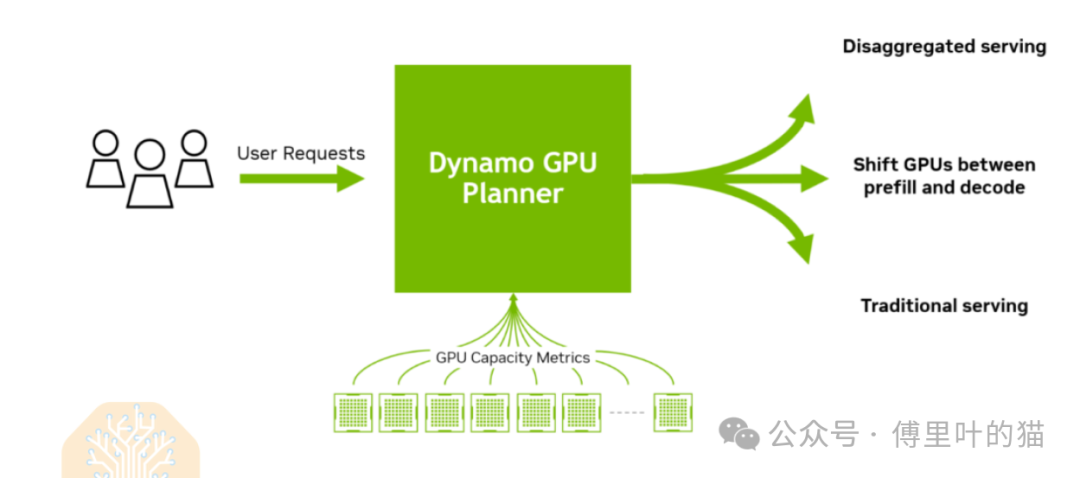

GPU规划器(GPU Planner)

GPU规划器是预填充和解码节点的自动扩展器,根据一天中自然波动的需求启动额外的节点。它可以在MoE(混合专家)模型中的许多专家之间实现一定程度的负载平衡,无论是预填充还是解码节点。GPU规划器会启动额外的GPU,为高负载专家提供额外的计算资源。它还可以根据需要动态重新分配预填充和解码节点之间的资源,进一步最大化资源利用率。

此外,它还支持调整用于解码和预填充的GPU比例——这对于像深度研究这样的用例特别有用,因为这些应用需要审查大量上下文,但只生成相对较少的输出。

12

改进的NCCL集体通信

(Improved NCCL Collective for Inference)

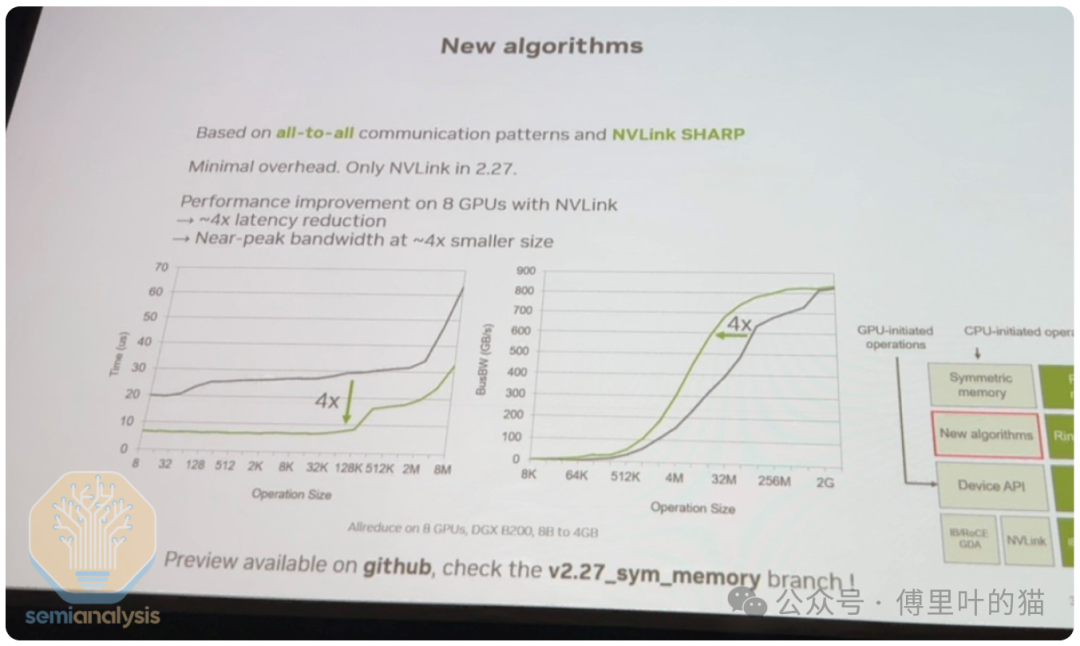

低延迟通信库是Nvidia集体通信库(NCCL)中的一组新算法,可以为较小的消息大小提供4倍更低的延迟——从而显著提升整体推理吞吐量。Sylvain详细阐述了这些改进——概述了实现这一提升的单次和双次全归约算法(one-shot and two-shot all-reduce algorithms)。由于AMD的RCCL库是NVIDIA NCCL的复制分支,Sylvain的NCCL重构将继续扩大CUDA的护城河,并导致AMD的RCCL花费数千个工程小时来同步Nvidia的重大重构。在AMD花费数千个工程小时同步Nvidia的更改时,Nvidia将利用这段时间继续推进集体通信软件栈和算法的前沿。

13

NIXL——NVIDIA推理传输引擎

(NIXL – NVIDIA Inference Transfer Engine)

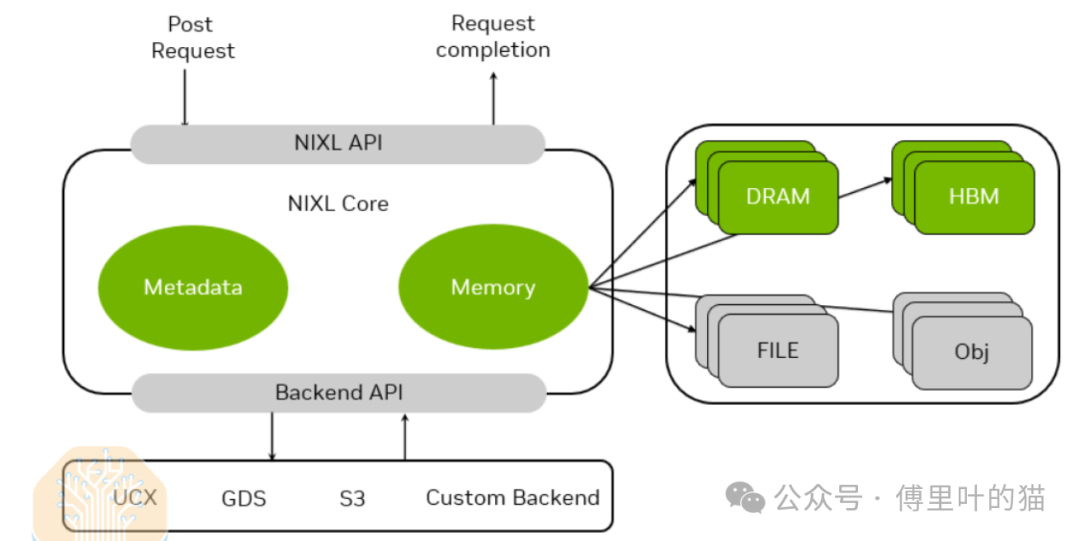

为了从预填充节点传输到解码节点,需要低延迟高带宽的通信传输库。NIXL将使用InfiniBand GPU异步初始化(IBGDA)。目前在NCCL中,控制流通过CPU代理线程,而数据流直接进入NIC,无需经过CPU缓冲。但使用IBGDA,控制流和数据流都不需要经过CPU,而是直接从GPU到NIC。NIXL还将抽象化CXL、本地NVMe、远程NVMe、CPU内存、远程GPU内存和GPU之间数据移动的复杂性。

14

NVMe KV缓存卸载管理器

(NVMe KV-Cache Offload Manager)

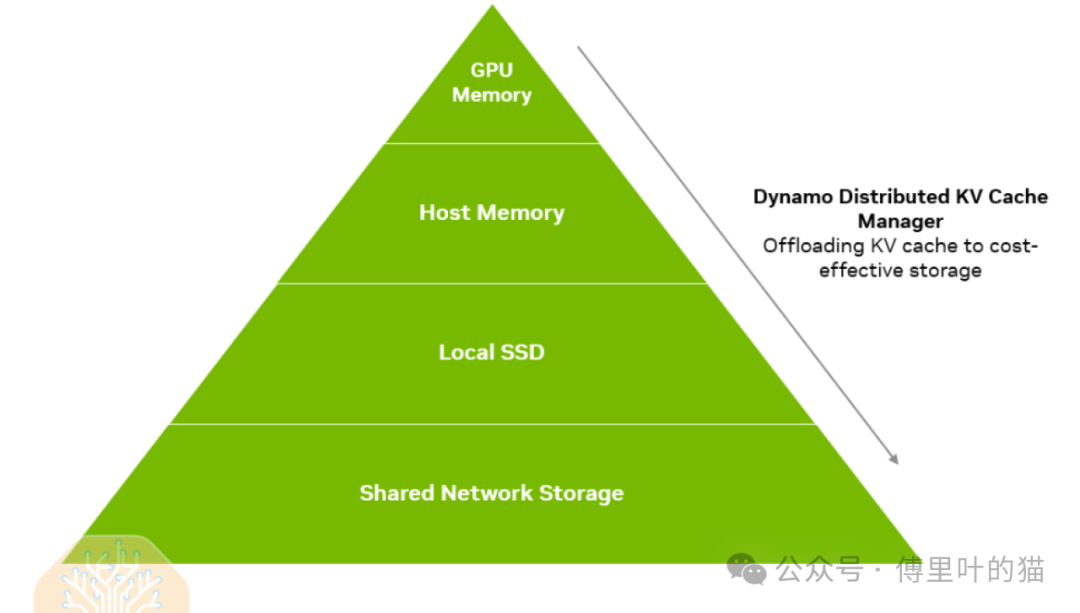

KV缓存卸载管理器通过将先前用户对话的KV缓存保存在NVMe存储中而不是丢弃它,从而更高效地执行整体预填充操作。

而通过NVMe KV缓存卸载,当用户暂时离开对话时,KV缓存可以被卸载到NVMe存储系统中,直到用户返回对话。当用户在对话中提出后续问题时,KV缓存可以快速从NVMe存储系统中检索出来,从而避免重新计算KV缓存。

这释放了预填充节点(prefill nodes)的容量,使其能够处理更多的输入量,或者可以减少预填充部署所需的规模。此外,由于检索KV缓存的时间远少于重新计算的时间,用户的体验也会显著提升,首次token生成时间(time to first token)会更快。

而通过NVMe KV缓存卸载,当用户暂时离开对话时,KV缓存可以被卸载到NVMe存储系统中,直到用户返回对话。当用户在对话中提出后续问题时,KV缓存可以快速从NVMe存储系统中检索出来,从而避免重新计算KV缓存。

这释放了预填充节点(prefill nodes)的容量,使其能够处理更多的输入量,或者可以减少预填充部署所需的规模。此外,由于检索KV缓存的时间远少于重新计算的时间,用户的体验也会显著提升,首次token生成时间(time to first token)会更快。

在DeepSeek的第六天GitHub笔记中,研究人员披露了磁盘上KV缓存的命中率为56.3%,这意味着其预填充部署的效率显著提升。我们了解到,在用户进行多轮对话时,这种部署的典型KV缓存命中率可能在50-60%之间。部署这种NVMe存储解决方案存在一定的成本,因此存在一个临界点,即对话足够短时,重新计算比重新加载更简单且更便宜,但在其他情况下,节省的成本是巨大的。

任何关注DeepSeek开源周的人都会对上述技术非常熟悉。上述链接无疑是快速了解这些技术的最佳途径,同时Nvidia也在加紧编写更多关于Dynamo的文档。所有这些功能的结果是推理性能的全面提升,令人印象深刻。Nvidia甚至讨论了在现有H100节点上部署Dynamo时的改进。本质上,Dynamo民主化了DeepSeek的创新,使社区中的每个人都能访问开源模型技术的最佳成果。这使得每个人,而不仅仅是拥有深厚推理部署工程团队的一流AI实验室,都能部署高效的推理系统。

最后,由于Dynamo广泛处理分散推理和专家并行性,它特别有助于单个复制和高交互性部署。当然,拥有许多节点是Dynamo充分发挥其能力并带来显著改进的前提。

15

AI总拥有成本——成本下降

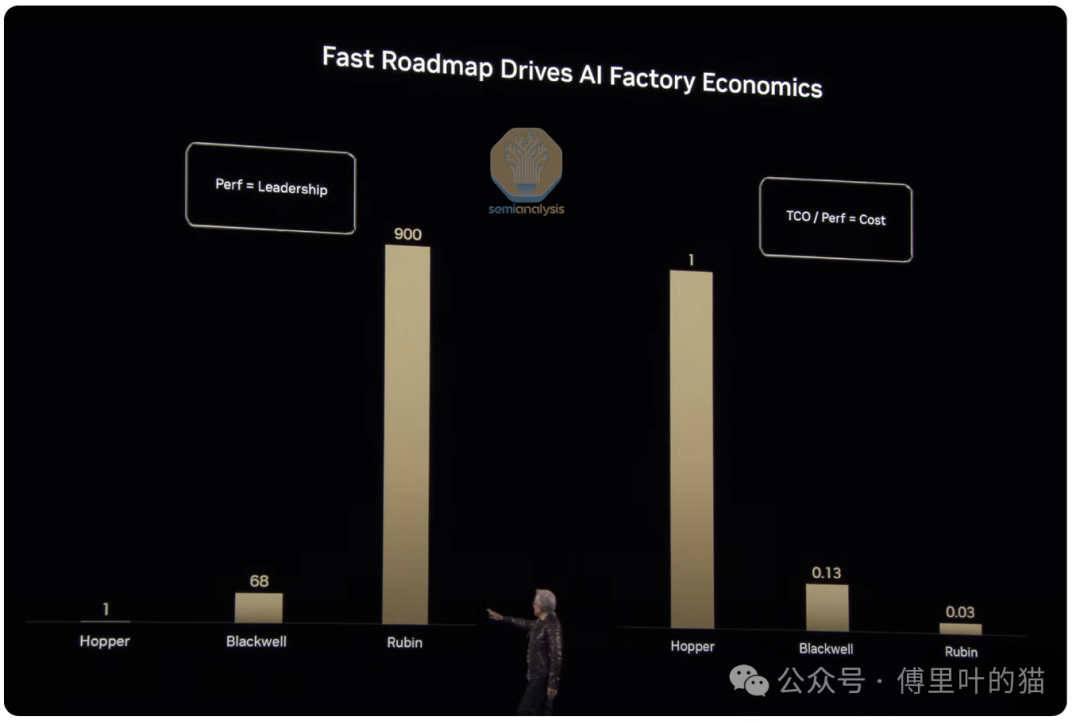

在结束对Blackwell的讨论后不久,Jensen通过讨论这些创新如何使他成为“首席收入破坏者”来强调这一点。他进一步指出,Blackwell的性能比Hopper提高了68倍,导致成本下降了87%。Rubin计划推动更多的性能提升——是Hopper的900倍,成本降低99.97%。

显然,Nvidia正在追求不懈的改进步伐——正如Jensen所说:“当Blackwell开始大量出货时,你甚至无法免费赠送Hopper。”

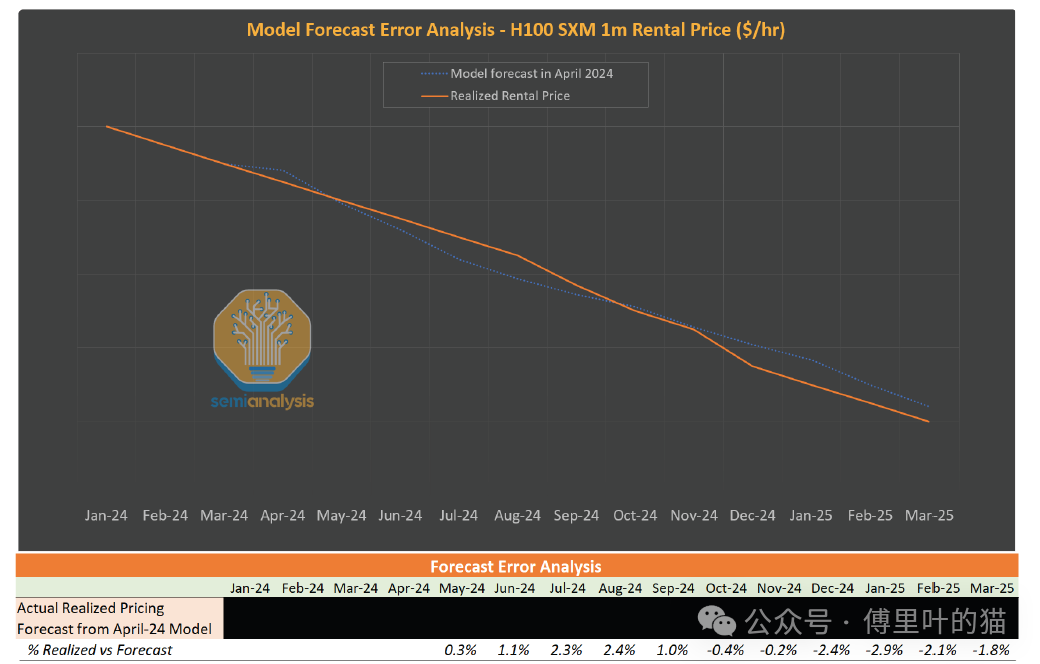

事实上,我们的H100租赁价格预测框架正是基于Jensen所阐述的观点。我们结合对未来安装基数、集群总拥有成本以及未来芯片能力的估计,构建了预测价格曲线。到目前为止,该框架具有指导意义。我们于2024年4月首次向客户发布了H100租赁价格预测模型——该模型从2024年初至今对H100租赁价格的预测准确率达到98%。

16

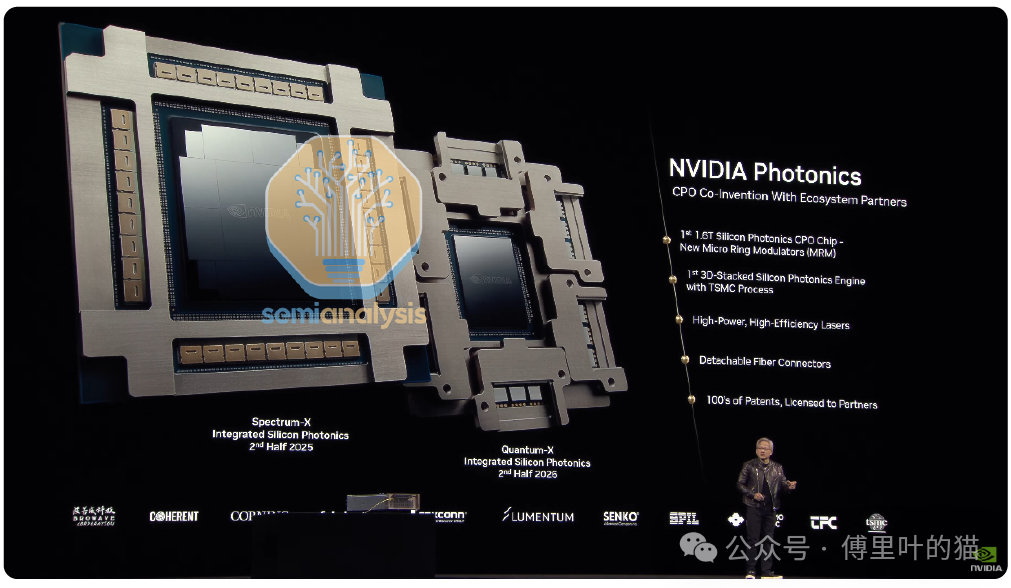

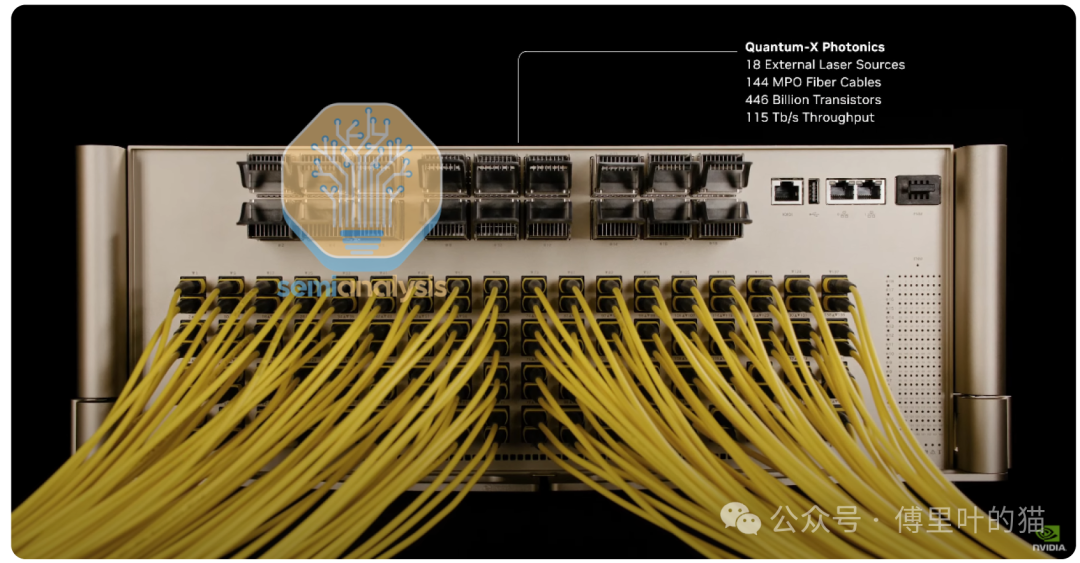

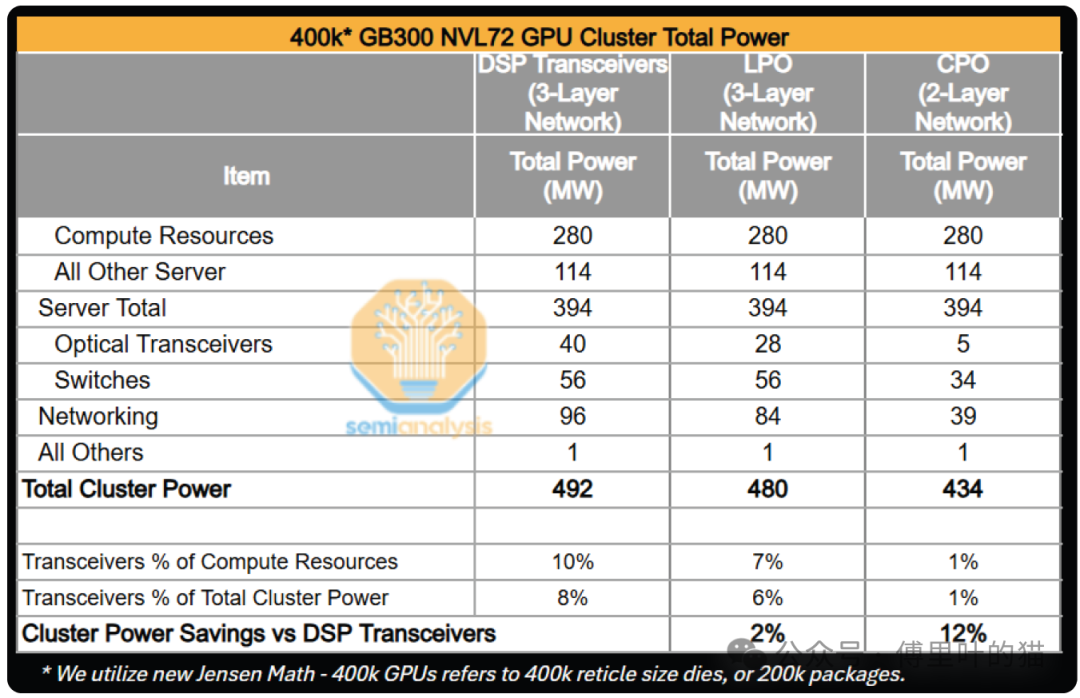

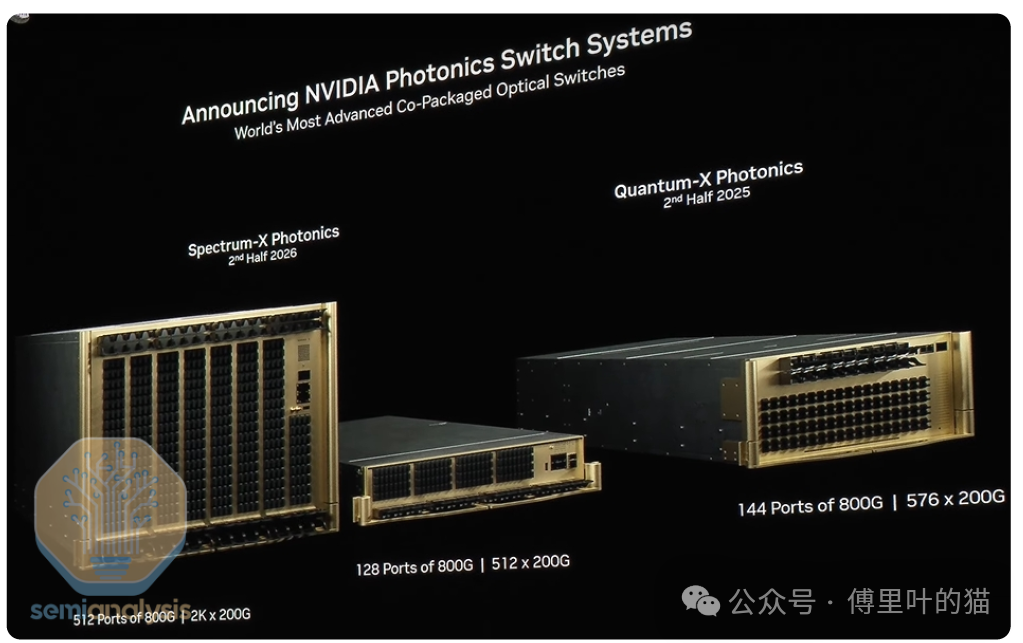

CPO Insertion

在主题演讲中,Nvidia宣布了其首款共封装光学(CPO)解决方案,将部署在其扩展交换机中。通过CPO,收发器被外部激光源(ELS)取代,这些激光源与直接放置在芯片硅片旁边的光学引擎(OE)一起促进数据通信。光纤电缆不再插入收发器端口,而是插入交换机上的端口,将信号直接路由到光学引擎。

Nvidia仍然是王者,并正在降低您的计算成本

今天,《Information》发表了一篇文章,称亚马逊将Trainium芯片定价为H100的25%。与此同时,Jensen正在谈论“在Blackwell全面推出后,你无法免费赠送H100”。我们认为后一种说法非常有力量。技术推动拥有成本,我们在各处(也许除了TPU)都看到了Nvidia路线图的模仿者。与此同时,Jensen正在推动技术的可能性。

新架构、机架结构、算法改进和CPO都是Nvidia与其竞争对手之间的技术差异。Nvidia今天在几乎所有方面都处于领先地位,当竞争对手赶上来时,他们又在另一个进步向量上推动前进。随着Nvidia继续其年度节奏,我们预计这种情况将继续下去。有人谈论ASIC是计算的未来,但我们从CPU时代看到,一个快速改进的通用平台是很难被击败的。Nvidia正在用GPU重新创建这个平台,我们预计他们将引领前沿。

祝您好运,跟上“首席收入破坏者”的步伐。

转载原创文章请添加微信:founderparker

内容中包含的图片若涉及版权问题,请及时与我们联系删除

评论

沙发等你来抢